설명

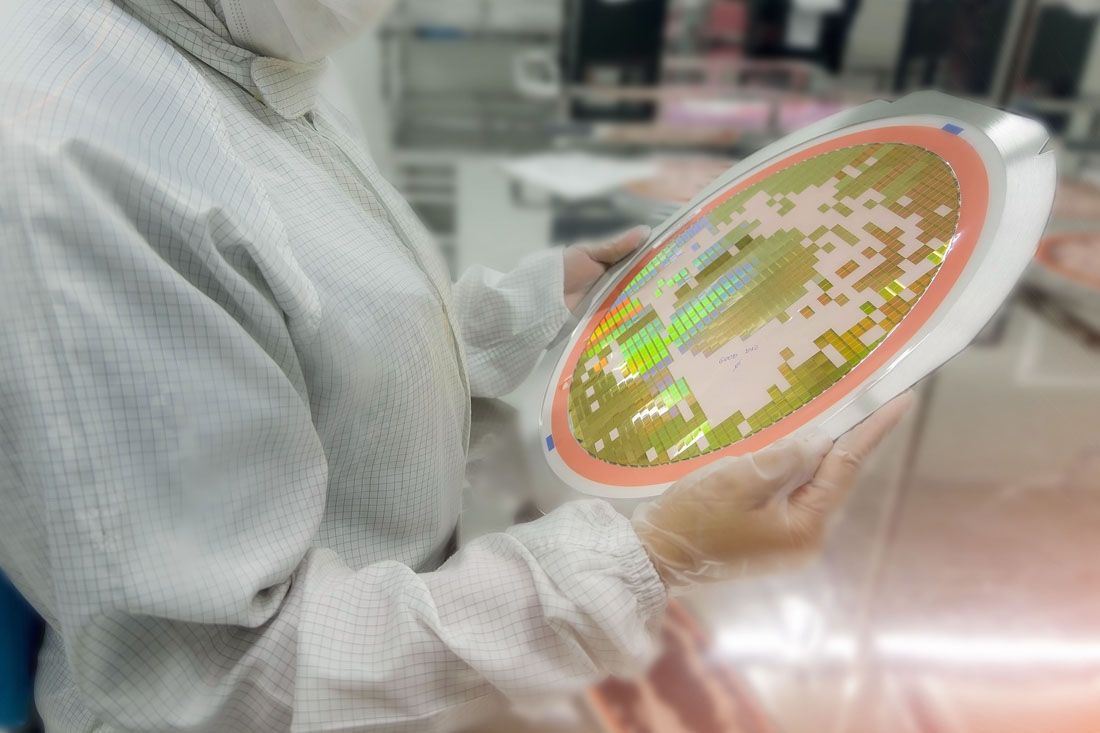

조립 전에 정확한 웨이퍼 두께를 얻는 것은 반도체 제조의 핵심 요소입니다. 웨이퍼 백 그라인딩(또는 웨이퍼 박형화)은 웨이퍼 두께를 제어하도록 설계된 반도체 제조 공정으로, 소형 전자 장치에서 적층되고 고밀도 패키징을 만드는 데 사용되는 초박형 웨이퍼를 생산하는 데 필수적입니다.

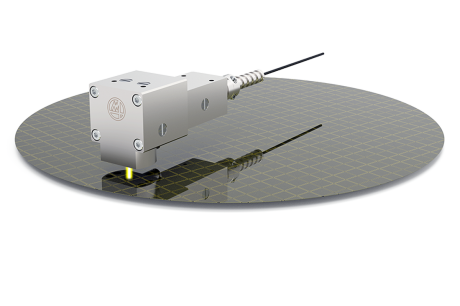

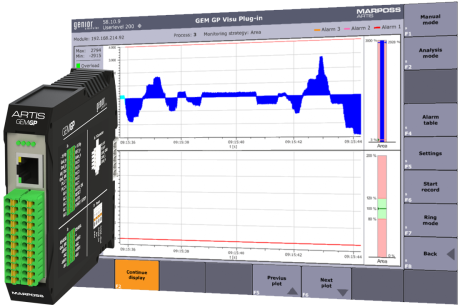

웨이퍼 박형은 항상 중요한 공정입니다. 칩은 이미 웨이퍼 위에 있으며 공정상의 모든 실패는 생산량과 비용에 영향을 미칩니다. DI 워터가 있는 경우에도 접촉 게이지 또는 비접촉 센서를 사용하여 박형 공정 시 엄격한 인라인 제어가 가능합니다.

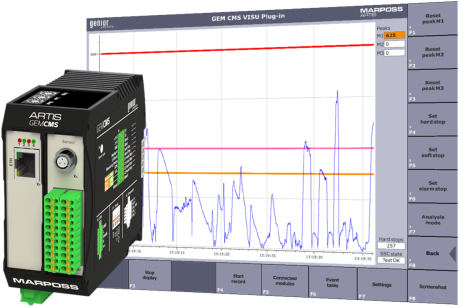

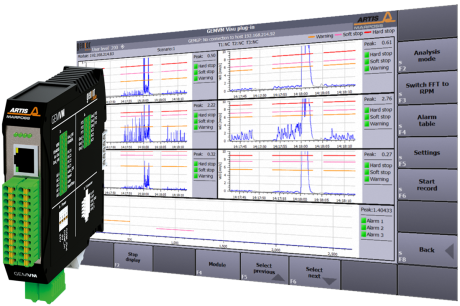

마르포스 센서를 적용하면 연삭 휠이 웨이퍼에 닿는 순간을 감지하거나 전력 과부하를 확인할 수도 있습니다.

장점

- 건조하고 습한 환경의 가공 공정 중에 신뢰할 수 있는 두께 측정

- 지지하는 테이프 또는 접착제의 유무에 영향을 받지 않는 측정

- 4 ~ 900µm 절대 두께 제어 (편측 측정)

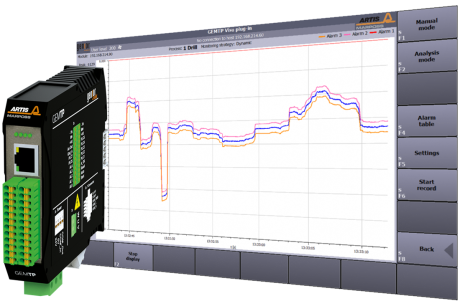

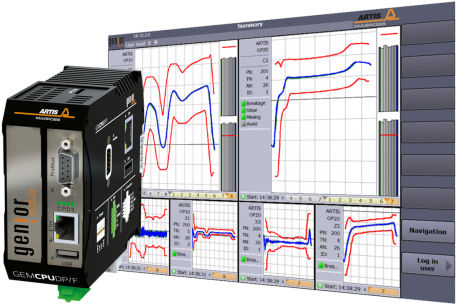

- 스마트하고 정교화된 두께를 위한 매우 얇은 두께 제어 및 데이터 로그 (블랙박스 기능)