ウェーハ検査プロセスの革命:AOP PCI 計測検査ソリューション

ウェーハ検査は半導体製造において重要な工程です。生産性の観点から見ると、損失のリスクを伴うだけでなく、さらに深刻な影響を伴う高額な品質問題の原因となることも知られています。

ウェーハ最終検査の課題

ウェーハの機能構造に関係する最終検査が終了すると、前工程 (FEOL) における価値創造段階が完了します。場合によっては、バンピングなどの後工程 (BEOL)がすでにウェーハに施されていることもあります。つまり、最終ウェーハ検査によって多数のコンポーネントが失われたり、ウェーハ全体が失われたりすると、製造工程の非常に遅い段階で製品の投資に大きな悪影響が生じることになります。

さらに状況を複雑にしているのは、多くの半導体メーカーがウェーハを自社内または外注での後工程を経ることなく、検査済みウェーハとして顧客に直接納品しているという事実です。つまり、前述の生産性の低下よりもさらに重大な可能性がある別の影響があるということです。最終ウェーハ検査中に、ウェーハが気付かぬうちに損傷してしまう可能性があります。過去には、このような損傷が原因で高額な製品リコールが発生した例が数多くあります。

プローブカード損傷への対処

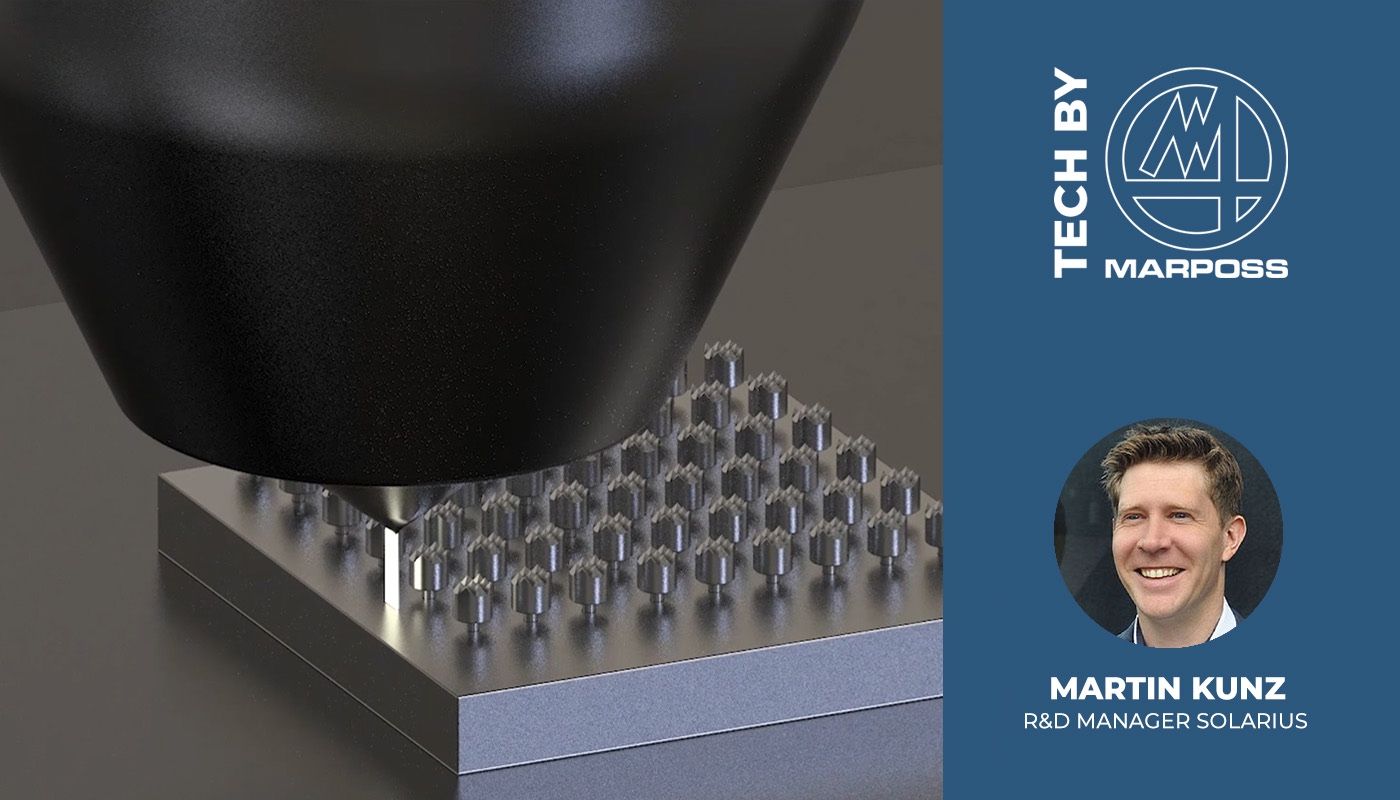

最終検査中に気付かない損傷を引き起こすことは数多くありますが、AOP PCI計測検査ツールがフォーカスするのは、欠陥のあるプローブカードによるウェーハの損傷です。欠陥のあるプローブカードが、最終ウェーハ検査中に大幅な生産性の低下を引き起こし、損傷に気付かない場合、予期しない結果を伴う製品リコールを引き起こす可能性があります。エンドユーザーへ出荷する前に検出され、確実に経済的損失を引き起こすプローブカード関連の損傷と比較すると、気付かれない損傷はウェーハが顧客に出荷される結果になります。これらの損傷したウェーハは最終的に発見されますが、生産ロットにすでに影響が出た後でのみ発見されます。

最悪のケースは、欠陥のあるコンポーネントが、複数の機能要素を含み、さらに高価なパッケージの一部になったときです。そして、最終パッケージ「システム」の最終テストまで損傷が検出されない場合、経済的損失はさらに大きくなります。これらのデバイスが自動車メーカーなどのエンドユーザーに出荷された場合の損失は言うまでもありません。このシナリオは大げさすぎるように思われるかもしれませんが、この事象は過去にも発生しており、欠陥のあるプローブカードが検出されなかったことが原因となっています。

上記より、財務的な影響や企業評価への影響を考慮すると、このような事態をどのように回避できるのでしょうか。

高速プローブカード検査プロセス

1つの方法として、プローブカードが検査に適しているかどうかを明確に判断する高速プローブカード検査工程を適用することです。ただし、このような考えは、実際のウェーハ検査には適用されていません。

したがって、暗黙の要件を詳しく見直す必要があります。つまり、テスト後にウェーハが無傷であることを保証するためには次の対応が必要です。

-

プローブカードを継続的かつ確実に観察し、不要な対象を特定します。これにより、ウェーハに刻印があるかどうかを判断できます。

- プローブチップの幾何学的パラメータを継続的かつ確実に観察します。これにより、プローブチップがウェーハ上のコンタクトパッドを正しく「引っ掻く」か「こする」かどうかを判断できます。

- 前述の状態とパラメータの観察は高速でなければならず、これによりプローブカードを頻繁にチェックおよび再チェックできるため、プロセス中のプローブカードの状態をクローズドループで観察できます。

プローブカードの調整から生じるウェーハへの損傷の可能性に関する情報に加えて、このようなプローブカード検査プロセスからプロセス制御関連情報も得ることができます。

プローブ先端の形状を正確に評価することで、先端がパッドとの良好な電気的接触のための適切な機械的前提条件を保証するかどうかを事前に判断できます。

プローブヘッドの形状を正確に評価することで、さまざまな「こすり」や「引っかき」動作につながるプローブヘッド表面の温度関連の変化について結論を出すことができます。

高速フィードバックにより、タッチダウンカウンターまたは処理された生産ロットの後プローブカードを頻繁に確認できます。

プローブ先端とプローブヘッドの状態に関する情報が継続的に利用可能であることは、テスト後に自動光学検査 (AOI) を実行する際、統計によって「こする」と相関関係にあると判断できます。これは、プローブヘッドに関して特に興味深いことです。「こする」または「引っかき」の動作は、基本的にプローブヘッドの形状と位置に依存するためです。

プロセスの迅速なフィードバックと詳細な障害情報により、集中的な修理およびメンテナンスサイクルの短縮が可能です。欠陥の性質と場所を迅速かつ明確に指摘でき、プローブカードがプロセスに戻される前に、プローブカードの完全な再評価を迅速に行うことができます。

AOP PCI 計測検査システム

Solarius(ソラリウス)は、前述の要件を満たすプロセスの必要性を十分に理解し、お客様と共同で、生産性の低下や品質問題につながる一般的な問題に対処するため、ウェーハテスト現場向けカスタムソリューションを開発しました。このコラボレーションの結果が、AOP PCI計測検査システムです。このツールにより、前述の要件に従ってウェーハテスト工程でプローブカードの全体的な状態を頻繁に評価する工程が可能になり、すべての主要なテスターインターフェースに適合します。AOP PCIツールは SEMI規格に従って設計されており、SECS/GEMインターフェースが組み込まれています。

本ツールは、既存のプローブカード解析ツールに準拠して動作するため、既存のプロセスに新しい情報や逸脱した情報を導入することはありません。AOP PCIには、ツール内で直接修復できるようにリワークステーションを装備することができ、プローブカードの OHTロードをサポートするためにアップサイドバージョンでのご提供も可能です。